## **University of New Mexico**

Department of Electrical and Computer Engineering

## ECE 321 – Electronics I (Fall 2009)

Exam 3

Name: Solution Date: Nov. 18, 2009

Note: Only calculator, pencils, and pens are allowed.

- (10 points) Fill in the blank: 1.

- (a) In standard CMOS process, the source and drain are formed by using pt and nt layer masks.

- (b) The process of manufacturing transistors is called <u>front-end</u> and the process of manufacturing interconnects is called <u>back-end</u>

- (c) CMP stands for <u>Chemical Mechanical Polishing</u>.

(d) The effective width of two series NMOS with W<sub>1</sub>=6um and W<sub>2</sub>=3um is <u>2µm</u>.

- (e) Electromigration is when metal latice atoms swept out of position by current density

- (20 points) You are asked to layout the power and ground bus in the layout of a 2. logic block in a real chip. Assume that the logic block draws 80mA of current and the metal thickness is 0.4 um. If the maximum current density  $J_{max} = 2x10^6 \text{ A/cm}^2$ , determine the minimum width (in micron) of the interconnect that is needed to power the logic block.

Jmax X Area = Current Area = width x thickness

$$J_{max} = 2 \times 10^{6} \text{ A/cm}^{2} \times \left(\frac{100 \text{ cm}}{1 \text{ m}}\right)^{2} \times \left(\frac{\text{im}}{1 \times 10^{6} \mu \text{m}}\right) = 0.02 \text{ A/m}^{2}$$

$$0.02 \text{ A/m}^{2} = \frac{80 \times 10^{-3} \text{ A}}{\text{Wx 0.4 \mu m}} \implies \text{W} = 10 \mu \text{m}$$

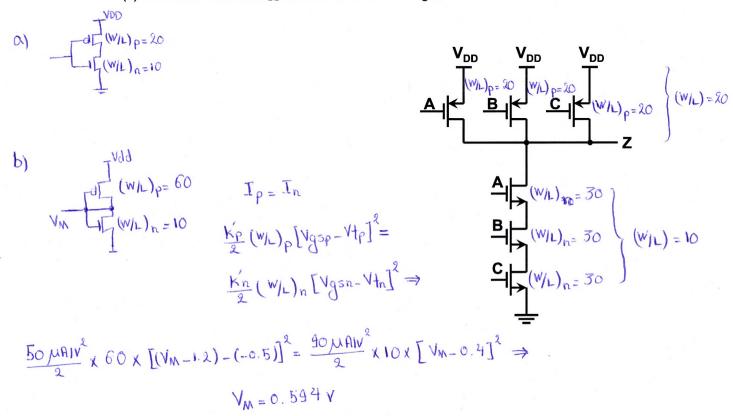

- 3. (30 points) A three-input CMOS NAND gate is designed as shown below. Assume that  $V_{DD}$ =1.2 V,  $K'_n$ =90 uA/V²,  $V_{tn}$ =0.4 V,  $K'_p$ =50 uA/V², and  $V_{tp}$ =-0.5 V in the 100nm technology node.

- (a) Determine the width of NMOS and PMOS transistors in this NAND gate, such that the worst case delay becomes equivalent to a referenced inverter with  $W_n$ =1um and  $W_o$ =2um.

- (b) For the device sizes found in part (a), determine the switching threshold voltage, V<sub>M</sub>, when all inputs are tied together.

- (c) Find the maximum I<sub>DD</sub> current for this NAND gate.

c)

$$I_{DD_{max}} = I_n(V_m) = \frac{40\mu\text{Alv}^2}{2}(10)[0.594-0.4]^2 \Rightarrow I_{DDMex} = 1.69x10^{-5}\text{A}$$

4. (40 points) We would like to design the following circuit such that the worst case propagation delays (t<sub>pHL</sub> and t<sub>pLH</sub>) are limited to 2.14 ns. Use Elmore delay equation to determine the W/L for PMOS and NMOS used in the 3-input NAND gate. Assume that V<sub>DD</sub>=1.2 V, K'<sub>n</sub>=90 uA/V<sup>2</sup>, V<sub>tn</sub>=0.4 V, K'<sub>p</sub>=50 uA/V<sup>2</sup>, and V<sub>tp</sub>=-0.5 V in the 100nm technology node. Also assume that the transistors stay in saturation region for the length of the transition.

$$T = \frac{t_{pLH}}{0.69}$$

$$T = (R+10K)\frac{1}{10} (R+10K+1K) \times (100^{4}F) + \frac{100^{4}F}{100^{4}F} + \frac{100^{$$