## **University of New Mexico**

**Department of Electrical and Computer Engineering**

## ECE 321L – Electronics I (Fall 2015) Homework #11

Due in class: Friday December 4, 2015

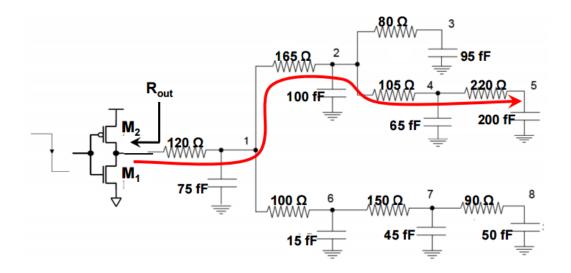

- 1. Assume that we have an inverter with  $V_{DD}$ =1.5 V,  $K'_n$ =100 uA/V²,  $V_{tn}$ =0.4 V,  $\lambda_n$ =0.1 V<sup>-1</sup>,  $(W/L)_n$ =10,  $K'_p$ =60 uA/V²,  $V_{tp}$ =-0.4 V,  $\lambda_p$ =0.2 V<sup>-1</sup>,  $(W/L)_p$ =17. Find  $R_{out}$ . Hint: connect a test capacitor of 100fF to the gate, calculate the LH propagation delay ( $t_{pLH}$ ) using average current technique, then equate the propagation delay to a simple RC network and find  $R_{out}$ . This will effectively be  $R_{out(LH)}$ .

- 2. We plan to use the inverter of problem 1 in the following circuit. Use Elmore technique to compute the time constant and LH propagation delay (t<sub>PLH</sub>) of the network from the gate input to node 5.

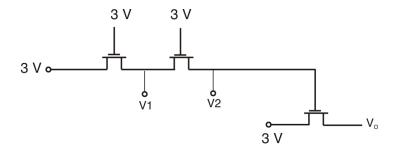

3. Assume that  $V_{T0}=0.5$  V,  $\gamma=0.3$  V<sup>1/2</sup>, and  $|\phi_f|=0.35$  V. Calculate the voltages at nodes: V<sub>1</sub>, V<sub>2</sub>, and V<sub>0</sub>. Considering the body effect for all transistors.

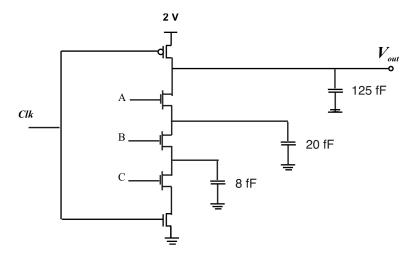

**4.** During the evaluate phase,  $V_A = V_B = 2 \text{ V}$ , and  $V_C = 0 \text{ V}$ . Use the charge sharing method, compute the final voltages at the  $V_{out}$  and 20 fF and 8 fF capacitors.

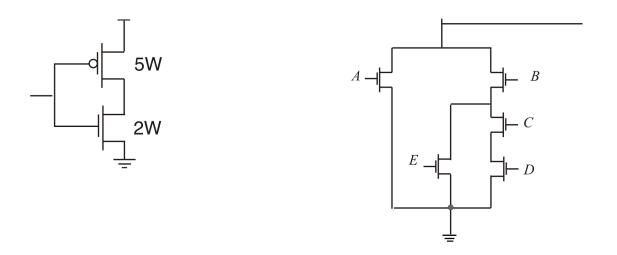

5. Sketch the pull up network, and write the scaling values on the schematic for all transistors with respect to the inverter. What is the Boolean function of this complex CMOS logic gate?

6. Compute the leakage power consumption in a CMOS inverter that is used in a clock distribution network of a digital circuit using 90nm technology node. Assume that the VDD is 1.2 V,  $I_{OFF(NMOS)}=12$  nA/um, and  $I_{OFF(PMOS)}=26$  nA/um,  $(W/L)_{p}=650$ ,  $(W/L)_{p}=950$ , and L=90nm.

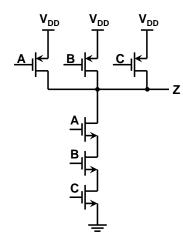

- 7. The following circuit is a 3 input NAND gate. Assume that  $V_{DD}$ =1.5 V,  $K'_n$ =100 uA/V²,  $V_{tn}$ =0.4 V,  $(W/L)_n$ =30,  $K'_p$ =60 uA/V²,  $V_{tp}$ =-0.4 V,  $(W/L)_p$ =20.

- **a.** If the load capacitance is 100fF, compute the propagation delay for each transition shown in the following table. For simplicity, assume that the transistors are in saturation for the whole length of the transition and neglect the body effect.

- **b.** Based on the propagation delays calculated in part a, find the effective output resistance of the NAND gate for each transition shown in the table blow.

| Transition (ABC)        | Propagation<br>Delay | Effective<br>Output<br>Resistance |

|-------------------------|----------------------|-----------------------------------|

| <b>000</b> → <b>111</b> |                      |                                   |

| 111 → 110               |                      |                                   |

| 111 → 100               |                      |                                   |

| 111 → 000               |                      |                                   |

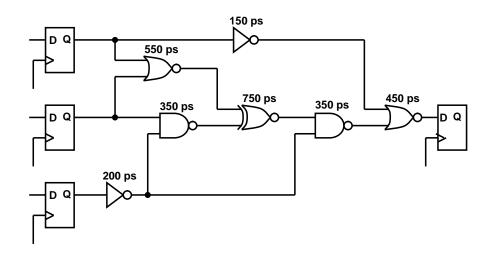

- **8.** Consider the following sequential circuit with 4 edge-triggered flip-flops and some logic gates. Assume that  $t_{SU} = 3$  ns,  $t_{hold} = 2$  ns, and  $t_{C2Q} = 1$  ns.

- (a) Identify the path with the maximum delay (critical path) on the schematic.

- (b) What is the maximum operating frequency of this circuit?

- (c) Identify the path with minimum delay on the schematic.

- (d) Does this circuit violate the hold time constraint? Why?

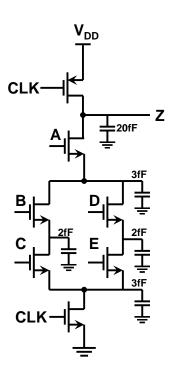

- **9.** The following circuit is a 4-input dynamic logic.

- (a) Identify the logic function for the output Z.

- (b) What input vector imposes the worst case charge sharing during the evaluation time?

- (c) Compute the final voltage at Z, if the input vector is ABCDE=11000 during evaluation after charge sharing. Assume that  $V_{tn} = 0.4V$ .

- (d) Determine the width of the PMOS such that the maximum worst case precharge time delay (0 to 90%) is limited to 250ps. (The worst case is when all the inputs are at  $V_{DD}$  such that all the intermediate capacitors contribute to the delay). Assume that  $V_{DD}$  = 1.2 V,  $K'_p$  = 50 uA/V², and  $V_{tp}$  = -0.5 V in the 100nm technology node. For simplicity assume that the PMOS will stay in saturation during the transition.

- 10. Dynamic logic design problem:

- (a) Draw the circuit diagram of a dynamic logic that performs  $Z = \overline{A + B(C + D)}$ .

- (b) Determine the width of NMOS transistors, such that the worst case  $t_{\text{pHL}}$  delay becomes roughly equivalent to a referenced inverter with  $W_n$ =1um and  $W_p$ =2um.