# **ECE321 – Electronics I**

# Lecture 12: CMOS Inverter: Noise Margin & Delay Model

#### Payman Zarkesh-Ha

Office: ECE Bldg. 230B

Office hours: Tuesday 2:00-3:00PM or by appointment

E-mail: payman@ece.unm.edu

ECE321 - Lecture 12

University of New Mexico

Slide: 1

#### Review of Last Lecture

- □ CMOS Inverter

- □ Voltage Transfer Characteristics (VTC)

- Switching threshold voltage

- Output high voltage

- Output low voltage

- Input high voltage

- Input low voltage

- □ Current Transfer Characteristics (ITC)

- Peak current

ECE321 - Lecture 12

University of New Mexico

# Today's Lecture

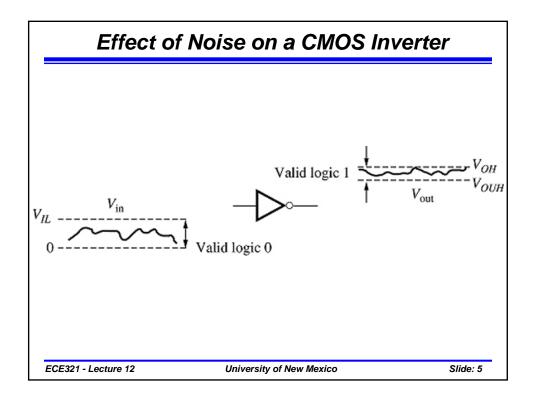

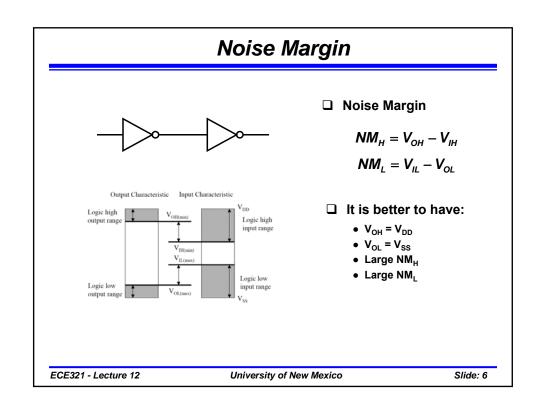

- Noise Margin Definition

- □ Approximation of Noise Margin for CMOS Inverter

- □ Propagation Delay

- □ Rise and Fall Times

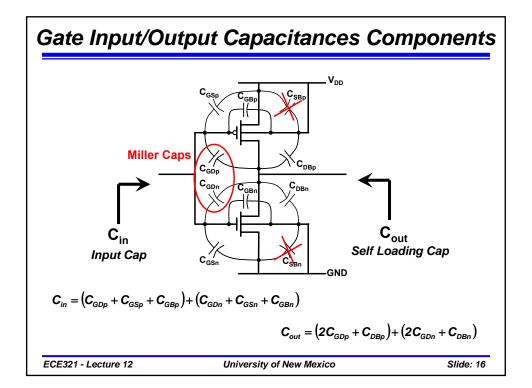

- ☐ Input and Self Loading (Load) Capacitances

- □ Delay Approximation

ECE321 - Lecture 12

University of New Mexico

Slide: 3

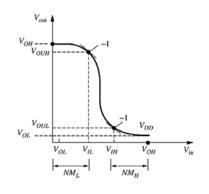

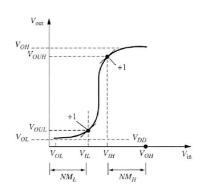

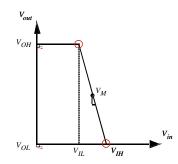

#### Review: Voltage Transfer Characteristics Low gain Important Parameters on VTC: $V_{OUH}$ Switching Threshold Voltage $V_{\rm S}$ or $V_{\rm M}$ Gain at V<sub>S</sub> or V<sub>M</sub> Output High Voltage V<sub>OH</sub> Output Low Voltage Vol $V_{OUL}$ Input High Voltage VIH $V_{IL}$ $V_{IH}$ Input Low Voltage V<sub>IL</sub> $V_S$ $V_{OH}$ $V_{IH}$ X (unknown) X (unknown) 0 Input range Output range ECE321 - Lecture 12 University of New Mexico Slide: 4

VTC of an inverter

VTC of a buffer

ECE321 - Lecture 12

University of New Mexico

Slide: 7

# Example: Noise Margin Calculation

An IC with  $V_{DD}=1.5$  V shows  $V_{OH}=1.35$  V,  $V_{OL}=0.2$  V,  $V_{IH}=1.2$  V, and  $V_{IL}=0.3$  V. Calculate the  $NM_L$  and  $NM_H$  for this IC.

Sketch the NM rectangles

$$NM_H = 1.35 - 1.2 = 150 \text{ mV}$$

$NM_L = 0.3 - 0.2 = 100 \text{ mV}$

ECE321 - Lecture 12

University of New Mexico

# Noise Margin Approximation

$V_{OH}$

$V_{OL}$

- ☐ How to compute Noise Margin

- Usually it is harder to compute the exact value of NM

- Use approximation (gain factor)

- Determine gain at V<sub>M</sub>

- Extrapolate V<sub>IL</sub> and V<sub>IH</sub>

- $\bullet~V_{\text{OL}}$  and  $V_{\text{OH}}$  are easy to compute

- □ Example:

- NM<sub>L</sub> and NM<sub>H</sub> in CMOS inverter

$$\begin{split} V_{IH} - V_{IL} &= -\frac{(V_{OH} - V_{OL})}{g} = \frac{-V_{DD}}{g} \\ V_{IH} &= V_{M} - \frac{V_{M}}{g} \qquad V_{IL} &= V_{M} + \frac{V_{DD} - V_{M}}{g} \\ NM_{H} &= V_{DD} - V_{IH} \qquad NM_{L} &= V_{IL} \end{split}$$

where

ECE321 - Lecture 12

$$g = \frac{-2}{\lambda_n + |\lambda_p|} \left( \frac{1}{V_M - V_{T_n}} + \frac{1}{V_{DD} - V_M - |V_{T_p}|} \right)$$

University of New Mexico

Slide: 9

# **Example: Noise Margin Approximation**

□ A CMOS inverter has  $V_{DD}$ =5V is designed to have  $V_{M}$ =2.9V. If  $V_{Tn}$ =0.7,  $V_{Tp}$ =-0.5,  $\lambda_{n}$ =0.05 V<sup>-1</sup> and  $\lambda_{p}$ =-0.08 V<sup>-1</sup>. Find the noise margins NMH and NML.

$$g = \frac{-2}{0.05 + 0.08} \left( \frac{1}{2.9 - 0.7} + \frac{1}{5 - 2.9 - 0.5} \right) = -16.6$$

$$V_{IL} = 2.9 + \frac{5 - 2.9}{-16.6} = 2.77 V$$

$$V_{IH} = 2.9 - \frac{2.9}{-16.6} = 3.1V$$

$$NMH = 5 - 3.1 = 1.9 V$$

$$NML = 2.77 - 0 = 2.77 V$$

ECE321 - Lecture 12

University of New Mexico

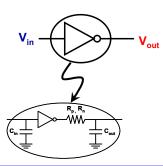

# **Dynamic Behavior of CMOS Inverter**

- ☐ Changing of the input doesn't instantaneously change the out pf an inverter

- ☐ This is mostly due to the time it takes to chrgae or dischage the output/load capacitor

- ☐ It is important to know how long it takes to get the signal out of the inverter or any CMOS logic gate

ECE321 - Lecture 12

University of New Mexico

Slide: 11

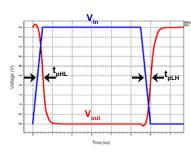

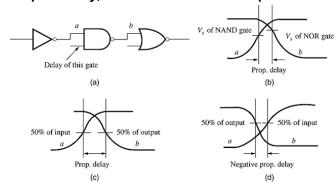

# **Definition: Propagation Delay**

- Definition of propagation delay

- is delay from where input crosses 50%Vdd to where output crosses 50%Vdd

- ullet Remember: the value of 50%Vdd is from switching threshold voltage (V<sub>M</sub>)

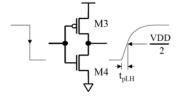

- t<sub>pHL</sub> is propagation delay when <u>output</u> switches from "High to Low"

- t<sub>pLH</sub> is propagation delay when <u>output</u> switches from "Low to High"

- ☐ To compute delay, the inverter must be simplified

ECE321 - Lecture 12

University of New Mexico

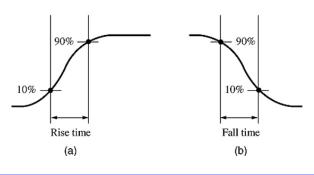

#### Definition: 10%-90% Rise/Fall Times

- ☐ Definition of 10%-90% rise time

- is delay from 10%Vdd to 90%Vdd in the output

- t, is the rise time when output switches from "Low to High"

- ☐ Definition of 90%-10% fall time

- is delay from 90%Vdd to 10%Vdd in the output

- t<sub>f</sub> is the fall time when output switches from "High to Low"

ECE321 - Lecture 12

University of New Mexico

Slide: 13

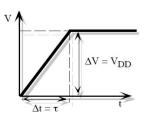

#### Definition: Linear Rise/Fall Times

- ☐ Definition of rise time (Hawkin's book)

- is delay from 0 to Vdd in the output assuming a constant current source model

- t<sub>r</sub> is the rise time when *output* switches from "Low to High"

- □ Definition of fall time (Hawkin's book)

- is delay from Vdd to 0 in the output assuming a constant current source model.

- t<sub>f</sub> is the fall time when output switches from "High to Low"

ECE321 - Lecture 12

University of New Mexico

# **Delay Calculation in CMOS Inveretr**

- ☐ It is not easy to accurately calculate delay in CMOS inverter, because

- CMOS inverter is a non-linear circuit, therefore exact delay calculation requires solving a non-linear differential equation

- Most of the elements in the circuit is voltage dependent (transistor drive current, parasitic capacitances, channel length modulation, etc.)

- □ A simplified model is required for basic calculations and design process

- □ Note that SPICE actually does solve the non-linear circuit accurately, but is only good for final verification, not the design

ECE321 - Lecture 12

University of New Mexico

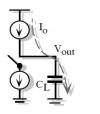

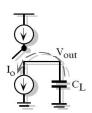

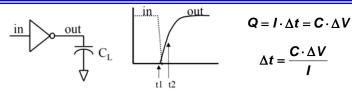

# **Propagation Delay Model**

- □ Propagation delay is defined as the time between the input reaching  $V_{DD}/2$  and the output reaching  $V_{DD}/2$

- $\Box$  To simplify the model, let's assume I is a constant I<sub>av</sub>

$t_{pLH} = t_2 - t_1 = \frac{C_L \cdot \left(V_{DD}/2\right)}{I_{av}}$

ECE321 - Lecture 12

University of New Mexico

Slide: 17

#### **Propagation Delay Model**

- $\square$  How to compute  $I_{av}$ ?

- Assume step input

- . NMOS goes into cutoff and stays there

- PMOS goes into saturation at first because  $|V_{DS}| > |V_{GS}| |V_T|$

- ullet PMOS will transition to linear, however, before  $V_{out}$  reaches  $V_{DD}/2$

$$I_{av} = \frac{I_{DS}(V_{out} = 0) + I_{DS}(V_{out} = V_{DD}/2)}{2}$$

pLH

$$I_{av} = \left(\frac{K_p'}{2}\right) \left(\frac{W_p}{L_p}\right) \left(\frac{\left(V_{DD} - \left|V_{vp}\right|\right)^2}{2} + \frac{V_{DD}\left(V_{DD} - \left|V_{vp}\right|\right)}{2} - \frac{{V_{DD}}^2}{8}\right)$$

ECE321 - Lecture 12

University of New Mexico

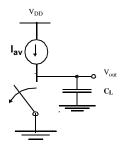

# **Propagation Delay Model**

□ A simpler model for I<sub>av</sub> can be obtained by assuming that the PMOS stays in saturation the whole time, therefore acts as an ideal current source

$$I_{av} = \left(\frac{K_p'}{2}\right) \left(\frac{W_p}{L_p}\right) \left(V_{DD} - \left|V_{tp}\right|\right)^2$$

$$t_{pLH} = t_2 - t_1 = \frac{C_L \cdot (V_{DD}/2)}{I_{av}} \quad \Rightarrow \quad t_{pLH} = \frac{C_L \cdot V_{DD}}{K_p' \left(\frac{W_p}{L_p}\right) (V_{DD} - |V_{Tp}|)^2}$$

$\square$  Assuming  $V_{DD} >> V_{Tp}$

$$t_{pLH} = \frac{C_L}{K_p' \left(\frac{W_p}{L_p}\right) V_{DD}}$$

☐ Same arguments hold for t<sub>pHL</sub>

ECE321 - Lecture 12

University of New Mexico

Slide: 19

#### Minimum Delay Design Techniques

- □ Reduce C<sub>in</sub> and C<sub>out</sub> Careful layout, keep drain diffusion area as small as possible

- □ Reduce wiring capacitance Careful layout, keep devices as close as possible

- □ Increase (W/L) of devices Need to be careful not to get into self-loading effect

- □ Increase V<sub>DD</sub> Need to be careful not to get into V<sub>DSAT</sub> or velocity saturation

ECE321 - Lecture 12

University of New Mexico

# Example: CMOS Inverter Delay

- □ A CMOS inverter has  $V_{DD}$ =5V is designed such that  $(W/L)_n$ =10 and  $(W/L)_p$ =20. Assume that  $V_{Tn}$ =0.7,  $V_{Tp}$ =-0.6,  $K'_n$ =100 uA/V²,  $K'_p$ =-60 uA/V², and the load capacitance is 100fF.

- 1) Use I $_{\rm av}$  model to find  $t_{\rm pHL},\,t_{\rm pLH},\,t_{\rm r(10\%-90\%)},$  and  $t_{\rm f(90\%-10\%)}.$

- 2) Use constant current source model to find  $t_{pHL},\,t_{pLH},\,t_{r(10\%-90\%)},\,t_{f(90\%-10\%)},\,t_r,$  and  $t_f.$

- □ Answers:

- 1)  $t_{pHL}$ =29.64 ps,  $t_{pLH}$ =23.73 ps,  $t_{r(10\%-90\%)}$ =56.71 ps, and  $t_{f(90\%-10\%)}$ =70.98 ps

- 2)  $t_{pHL}$ =27.04 ps,  $t_{pLH}$ =21.52 ps,  $t_{r(10\%-90\%)}$ =34.43 ps, and  $t_{r(90\%-10\%)}$ =43.27 ps,  $t_r$ =43.04 ps and  $t_r$ =54.98 ps.

ECE321 - Lecture 12

University of New Mexico