# **ECE321 – Electronics I**

# Lecture 8: MOSFET Threshold Voltage and Parasitic Capacitances

#### Payman Zarkesh-Ha

Office: ECE Bldg. 230B

Office hours: Tuesday 2:00-3:00PM or by appointment

E-mail: payman@ece.unm.edu

ECE321 - Lecture 8

University of New Mexico

Slide: 1

#### Review of Last Lecture

- □ Device Model for Linear Region

- □ Device Model for Saturation Region

- □ Channel Length Modulation

ECE321 - Lecture 8

University of New Mexico

# Today's Lecture

- ☐ Threshold Voltage Equation

- ☐ "Dynamic Parameters of Long Channel MOSFET"

- MOSFET Parasitic Capacitances

- Overlap capacitances

- Channel capacitances

- Junction capacitances

ECE321 - Lecture 8

University of New Mexico

Slide: 3

# Threshold Voltage Equation

- MOSFET is a four terminal device; Gate, Source, Drain, and Bulk.

- ☐ The Bulk may not be always connected to the Source.

ECE321 - Lecture 8

University of New Mexico

#### Threshold Voltage Equation

- □ We normally assume that the bulk of the MOSFET is connected to source. However, sometimes the bulk and source are in different potentials ( $V_{SB} \neq 0$ ).  $V_{SB}$  is called "body bias".

- $\Box$  The applied  $V_{SB}$  changes the threshold voltage as shown below:

$$oldsymbol{V_T} = oldsymbol{V_{T0}} + \gamma igg( \sqrt{ig| 2arphi_F + oldsymbol{V_{SB}}ig|} - \sqrt{ig| 2arphi_Fig|} igg)$$

$\Box$  In this equation,  $V_{\tau 0}$  is the zero bias threshold voltage,  $\gamma$  is the body bias coefficient, and  $\phi_F$  is:

$$\varphi_{F} = \frac{KT}{q} Ln \left( \frac{N_{A}}{n_{i}} \right)$$

$\Box$  Where  $N_A$  is the doping concentration in the substrate.

ECE321 - Lecture 8

University of New Mexico

Slide: 5

#### Example: Threshold Voltage & Body Bias

$\Box$  Assume that V<sub>T0</sub>=0.8V,  $\gamma$ =0.6 V<sup>1/2</sup>,  $\phi_F$ = 0.4 V. Find V<sub>T</sub> if V<sub>SB</sub>= 2.5 V

$$V_{T} = V_{T0} + \gamma \left( \sqrt{2\varphi_{F} + V_{SB}} - \sqrt{2\varphi_{F}} \right)$$

$$V_{\tau} = 0.8 + 0.6 \times \left( \sqrt{|2 \times 0.4 + 2.5|} - \sqrt{|2 \times 0.4|} \right) = 0.8 + 0.55 = 1.35$$

Observations:

- 1) Body bias is normally reverse bias. (why?)

- 2) More reverse body bias increases the threshold voltage.

ECE321 - Lecture 8

University of New Mexico

#### **MOSFET Threshold Voltage**

- The gate potential at which the channel inverts is called the threshold voltage (V<sub>T</sub>)

- V<sub>T</sub> is always referenced in relation to the gate to source potential V<sub>GS</sub> (this is because the surface potential needs to exceed the source to "lure" electrons away into the channel)

- V<sub>T</sub> is comprised of four main components:

- Work function difference between the gate and substrate  $\phi_F(substrate) \phi_F(gate)$

- $V_{GS}$  component required to change the surface potential of  $2\varphi_{F}$

- $V_{GS}$  needed to offset the depletion region charge

- V<sub>GS</sub> needed to offset charges trapped in the gate oxide

ECE321 - Lecture 8

University of New Mexico

Slide: 7

#### More Detail on MOSFET Threshold Voltage

Zero body bias threshold voltage:  $V_{T0} = \varphi_{ms} + 2\varphi_F + \frac{\sqrt{2qN_A\varepsilon_{si}}|2\varphi_F|}{C_{ox}} - \frac{Q_{ox}}{C_{ox}}$

Where:  $\varphi_F = \frac{KT}{q} Ln \left( \frac{N_A}{n_i} \right)$  and  $C_{ox} = \frac{\varepsilon_{ox}}{t_{ox}}$

Threshold voltage with body bias:  $V_T = V_{T0} + \gamma \left( \sqrt{|2\varphi_F + V_{SB}|} - \sqrt{|2\varphi_F|} \right)$

Where:  $\gamma = \frac{\sqrt{2qN_A \epsilon_{si}}}{C_{ox}}$

**Important Facts:**

- · Body bias increases threshold voltage

- Threshold voltage is positive for normal NMOS

- Threshold voltage is negative for normal PMOS

ECE321 - Lecture 8

University of New Mexico

### **MOS Capacitance**

- □ Delay of digital CMOS circuits depends of capacitance of MOS device

- ☐ There is a trade off between parasitic capacitance and drive strength of MOS device

- $\bullet~$  Larger  $\mathbf{C}_{\mathrm{ox}}$  increases the drive strength (I\_{DS} equation)

- $\bullet\,$  However, larger  $\mathbf{C}_{\mathrm{ox}}$  increases the device parasitic capacitance

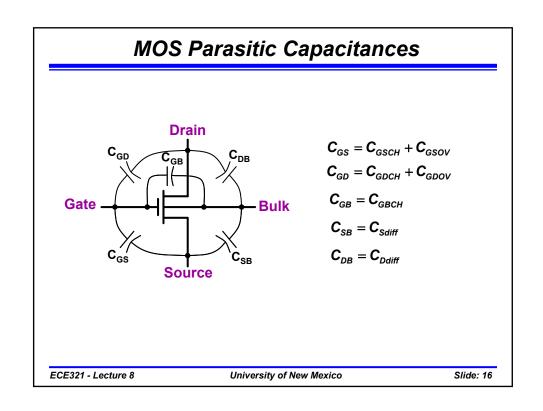

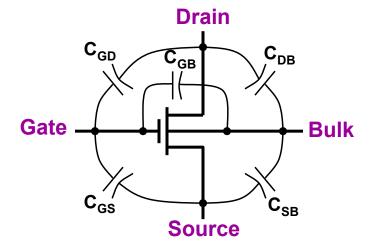

- MOS parasitic capacitance includes

- Overlap capacitances

- · Channel capacitances

- Junction capacitances

- Between almost every two terminals of MOS device, there is a source of parasitic capacitance

ECE321 - Lecture 8

University of New Mexico

Slide: 9

# MOS Parasitic Capacitances

ECE321 - Lecture 8

University of New Mexico

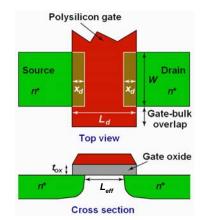

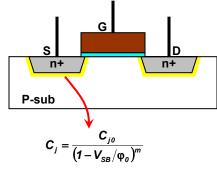

- □ Because of the lateral S/D diffusion, there is an overlap between gate and S/D junctions

- ☐ This overlap capacitance is a constant linear capacitance

$$C_{GSOV} = C_{GDOV} = WC_{ox}X_{d}$$

ECE321 - Lecture 8

University of New Mexico

Slide: 11

# **Channel Capacitances**

☐ Channel capacitance is a voltage dependent and non-linear capacitance

0

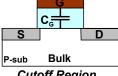

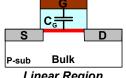

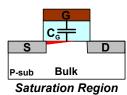

**Cutoff Region**

**Operation Region**

Cutoff

Linear

Saturation

Linear Region

$C_{GBCH}$  $C_{GSCH}$  $C_{GDCH}$  $C_{ox}WL_{eff}$ 0 0 C<sub>ox</sub>WL<sub>eff</sub>  $C_{ox}WL_{eff}$ 0

C<sub>ox</sub>WL<sub>eff</sub>

ECE321 - Lecture 8

University of New Mexico

0

$$C_{jo} = A_D \sqrt{\left(\frac{\varepsilon_{si} q}{2} \frac{N_A N_D}{N_A + N_D}\right) \varphi_o^{-1}} \qquad \qquad \varphi_o = \frac{KT}{q} Ln \left(\frac{N_D}{N_D} \right)$$

ECE321 - Lecture 8

diode)

University of New Mexico

Slide: 13

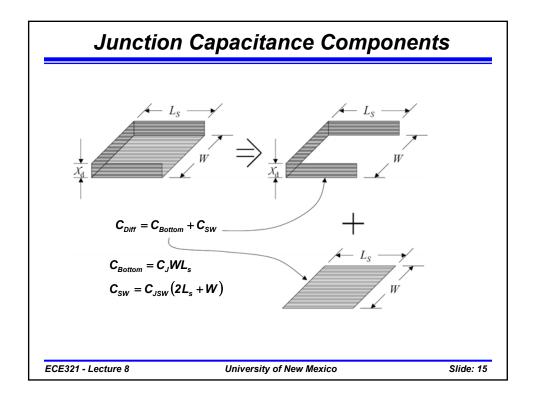

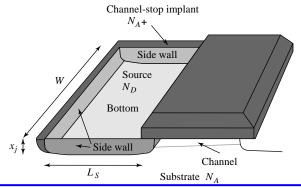

# **Junction Capacitance Components**

- The Junction capacitance of bottom plate is treated separately from the three non-gate edges

- The gate edge is often ignored since it is part of the conducting channel

- The bottom plate is usually step graded with m=0.5

- The sidewall are step graded with m=0.33 and face the channel-stop implant which has much higher doping than substrate

ECE321 - Lecture 8

University of New Mexico